ПЛИС Cyclone 4 как mapper для Dendy картриджа

Posted: Sat Feb 18, 2017 6:04 pm

Решил попробовать собрать свой картридж для Dendy. Mapper реализовывать буду на Cyclone 4 EP4CE10F17C0N. Много ног. Много вентилей. Но 3,3В максимум для логики.

Начинаю с UNROM так как имею опыт повторения его на стандартной логике.

В качестве ПЗУ - AM29F010B. ОЗУ - HM6264LP-12.

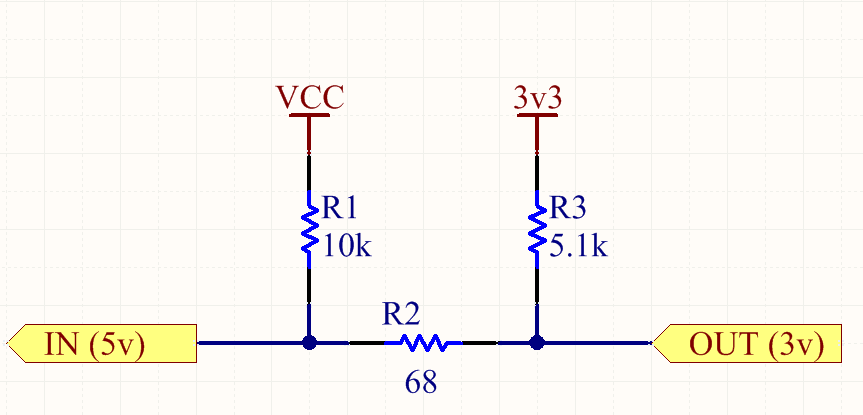

Соответственно возникает проблема согласования логических уровней. Нашел статью "Согласование логических уровней 5В и 3.3В устройств"

http://we.easyelectronics.ru/Shematech/ ... oystv.html

Остановился на варианте с буферной микросхемой LVC244A. Выходы со слота картриджа буду заводить на ПЛИС через нее. Но вопрос: можно ли напрямую заводить выводы ПЛИС на адресные линии ПЗУ картриджа? Ведь получается что часть адресной шины ПЗУ будет управляться с приставки 5В сигналом, а часть с ПЛИС 3,3В сигналом.

Более общий вопрос: можно ли смешивать различные способы согласования в одной схеме? То есть на шину данных поставить трансивер, а на прочие выводы - буферную микросхему.

Начинаю с UNROM так как имею опыт повторения его на стандартной логике.

В качестве ПЗУ - AM29F010B. ОЗУ - HM6264LP-12.

Соответственно возникает проблема согласования логических уровней. Нашел статью "Согласование логических уровней 5В и 3.3В устройств"

http://we.easyelectronics.ru/Shematech/ ... oystv.html

Остановился на варианте с буферной микросхемой LVC244A. Выходы со слота картриджа буду заводить на ПЛИС через нее. Но вопрос: можно ли напрямую заводить выводы ПЛИС на адресные линии ПЗУ картриджа? Ведь получается что часть адресной шины ПЗУ будет управляться с приставки 5В сигналом, а часть с ПЛИС 3,3В сигналом.

Более общий вопрос: можно ли смешивать различные способы согласования в одной схеме? То есть на шину данных поставить трансивер, а на прочие выводы - буферную микросхему.